16K X2816C 2048 x 8 Bit

# 5 Volt, Byte Alterable E<sup>2</sup>PROM

### **FEATURES**

- 90ns Access Time

- Simple Byte and Page Write

- —Single 5V Supply

- —No External High Voltages or V<sub>PP</sub> Control Circuits

- -Self-Timed

- -No Erase Before Write

- -No Complex Programming Algorithms

- -No Overerase Problem

- High Performance Advanced NMOS Technology

- Fast Write Cycle Times

- —16 Byte Page Write Operation

- -Byte or Page Write Cycle: 5ms Typical

- -Complete Memory Rewrite: 640ms Typical

- —Effective Byte Write Cycle Time: 300μs

Typical

- DATA Polling

- -Allows User to Minimize Write Cycle Time

- JEDEC Approved Byte-Wide Pinout

- High Reliability

- Endurance: 10,000 CyclesData Retention: 100 Years

## **DESCRIPTION**

The Xicor X2816C is a 2K x 8 E<sup>2</sup>PROM, fabricated with an advanced, high performance N-channel floating gate MOS technology. Like all Xicor Programmable nonvolatile memories it is a 5V only device. The X2816C features the JEDEC approved pinout for byte-wide memories, compatible with industry standard RAMs, ROMs and EPROMs.

The X2816C supports a 16-byte page write operation, typically providing a  $300\mu s/byte$  write cycle, enabling the entire memory to be written in less than 640ms. The X2816C also features  $\overline{DATA}$  Polling, a system software support scheme used to indicate the early completion of a write cycle.

Xicor E<sup>2</sup>PROMs are designed and tested for applications requiring extended endurance. Inherent data retention is greater than 100 years.

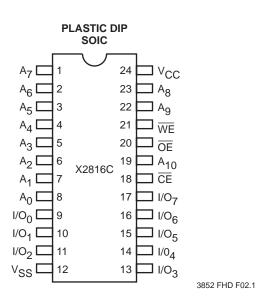

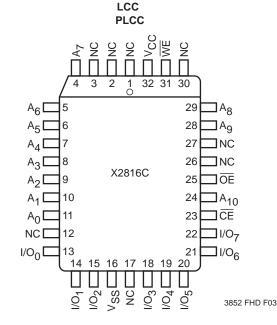

#### PIN CONFIGURATION

#### **PIN DESCRIPTIONS**

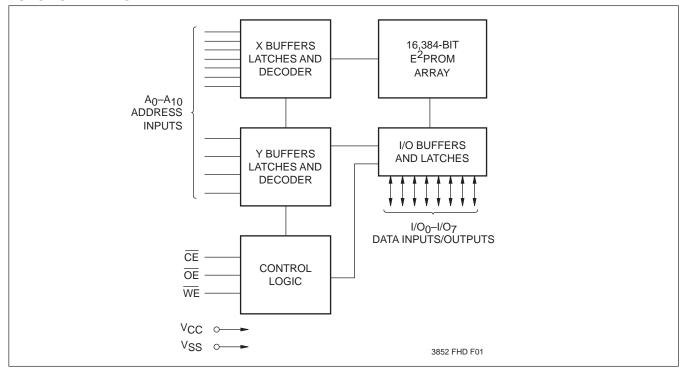

# Addresses (A<sub>0</sub>-A<sub>10</sub>)

The Address inputs select an 8-bit memory location during a read or write operation.

# Chip Enable (CE)

The Chip Enable input must be LOW to enable all read/write operations. When  $\overline{\text{CE}}$  is HIGH, power consumption is reduced.

# Output Enable (OE)

The Output Enable input controls the data output buffers and is used to initiate read operations.

#### **PIN NAMES**

| Symbol                             | Description       |

|------------------------------------|-------------------|

| A <sub>0</sub> -A <sub>10</sub>    | Address Inputs    |

| I/O <sub>0</sub> –I/O <sub>7</sub> | Data Input/Output |

| WE                                 | Write Enable      |

| CE                                 | Chip Enable       |

| ŌĒ                                 | Output Enable     |

| Vcc                                | +5V               |

| Vss                                | Ground            |

| NC                                 | No Connect        |

3852 PGM T01

## **FUNCTIONAL DIAGRAM**

#### **DEVICE OPERATION**

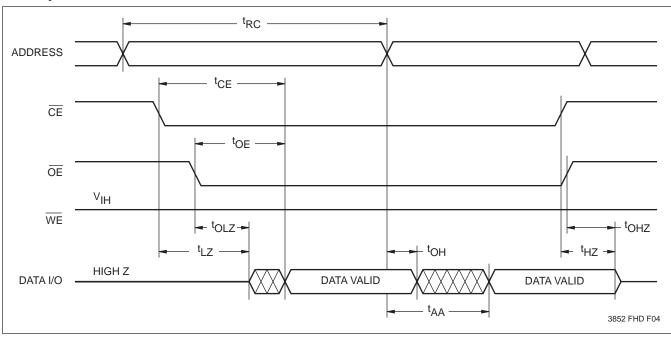

#### Read

Read operations are initiated by both  $\overline{OE}$  and  $\overline{CE}$  LOW and  $\overline{WE}$  HIGH. The read operation is terminated by either  $\overline{CE}$  or  $\overline{OE}$  returning HIGH. This two line control architecture eliminates bus contention in a system environment. The data bus will be in a high impedance state when either  $\overline{OE}$  or  $\overline{CE}$  is HIGH.

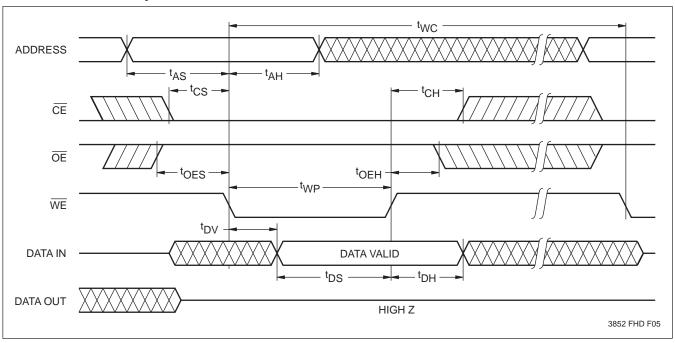

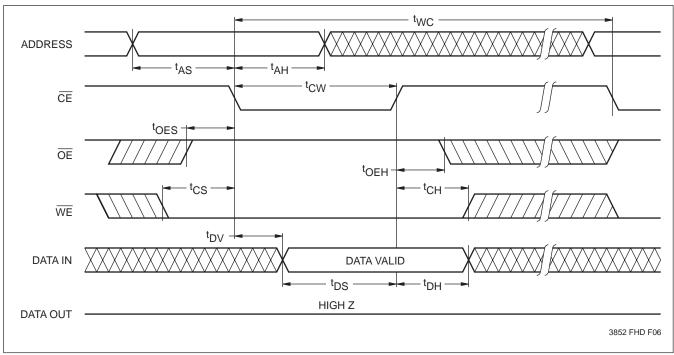

### Write

Write operations are initiated when both  $\overline{CE}$  and  $\overline{WE}$  are LOW and  $\overline{OE}$  is HIGH. The X2816C supports both a  $\overline{CE}$  and  $\overline{WE}$  controlled write cycle. That is, the address is latched by the falling edge of either  $\overline{CE}$  or  $\overline{WE}$ , whichever occurs last. Similarly, the data is latched internally by the rising edge of either  $\overline{CE}$  or  $\overline{WE}$ , whichever occurs first. A byte write operation, once initiated, will automatically continue to completion, typically within 5ms.

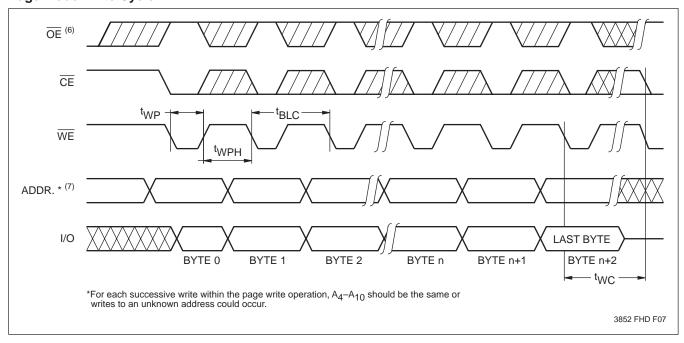

## **Page Write Operation**

The page write feature of the X2816C allows the entire memory to be typically written in 640ms. Page write allows two to sixteen bytes of data to be consecutively written to the X2816C prior to the commencement of the internal programming cycle. Although the host system may read data from any other device in the system to transfer to the X2816C, the destination page address of the X2816C should be the same on each subsequent strobe of the  $\overline{\text{WE}}$  and  $\overline{\text{CE}}$  inputs. That is,  $A_4$  through  $A_{10}$  must be the same for each transfer of data to the X2816C during a page write cycle.

The page write mode can be entered during any write operation. Following the initial byte write cycle, the host can write an additional one to fifteen bytes in the same manner as the first byte was written. Each successive

byte load cycle, started by the  $\overline{WE}$  HIGH to LOW transition, must begin within 20µs of the falling edge of the preceding  $\overline{WE}$ . If a subsequent  $\overline{WE}$  HIGH to LOW transition is not detected within 20µs, the internal automatic programming cycle will commence. There is no page write window limitation. The page write window is infinitely wide, so long as the host continues to access the device within the byte load cycle time of 20µs.

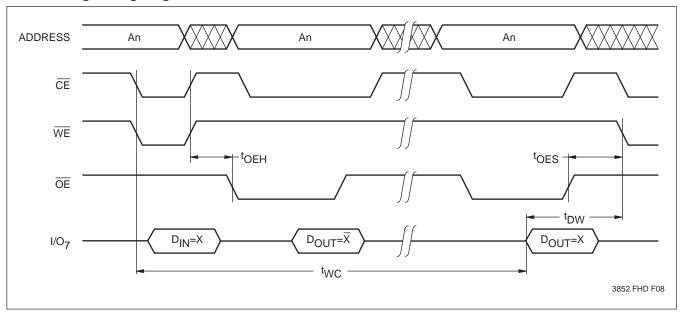

### DATA Polling

The X2816C features  $\overline{DATA}$  Polling as a method to indicate to the host system that the byte write or page write cycle has completed.  $\overline{DATA}$  Polling allows a simple bit test operation to determine the status of the X2816C, eliminating additional interrupt inputs or external hardware. During the internal programming cycle, any attempt to read the last byte written will produce the complement of that data on I/O<sub>7</sub> (i.e., write data = 0xxx xxxx, read data = 1xxx xxxxx). Once the programming cycle is complete, I/O<sub>7</sub> will reflect true data.

#### WRITE PROTECTION

There are three features that protect the nonvolatile data from inadvertent writes.

- Noise Protection—A WE pulse which is typically less than 10ns will not initiate a write cycle.

- V<sub>CC</sub> Sense—All functions are inhibited when V<sub>CC</sub> is ≤3V, typically.

- Write Inhibit—Holding either OE LOW, WE HIGH, or CE HIGH during power-up and power-down, will inhibit inadvertent writes. Write cycle timing specifications must be observed concurrently.

#### **ENDURANCE**

Xicor E<sup>2</sup>PROMs are designed and tested for applications requiring extended endurance.

# X2816C

#### SYSTEM CONSIDERATIONS

Because the X2816C is frequently used in large memory arrays, it is provided with a two line control architecture for both read and write operations. Proper usage can provide the lowest possible power dissipation and eliminate the possibility of contention where multiple I/O pins share the same bus.

To gain the most benefit, it is recommended that  $\overline{\text{CE}}$  be decoded from the address bus and be used as the primary device selection input. Both  $\overline{\text{OE}}$  and  $\overline{\text{WE}}$  would then be common among all devices in the array. For a read operation this assures that all deselected devices are in their standby mode and that only the selected device(s) is outputting data on the bus.

Because the X2816C has two power modes, standby and active, proper decoupling of the memory array is of

prime concern. Enabling  $\overline{\text{CE}}$  will cause transient current spikes. The magnitude of these spikes is dependent on the output capacitive loading of the I/Os. Therefore, the larger the array sharing a common bus, the larger the transient spikes. The voltage peaks associated with the current transients can be suppressed by the proper selection and placement of decoupling capacitors. As a minimum, it is recommended that a  $0.1\mu\text{F}$  high frequency ceramic capacitor be used between  $V_{\text{CC}}$  and  $V_{\text{SS}}$  at each device. Depending on the size of the array, the value of the capacitor may have to be larger.

In addition, it is recommended that a  $4.7\mu F$  electrolytic bulk capacitor be placed between  $V_{CC}$  and  $V_{SS}$  for each eight devices employed in the array. This bulk capacitor is employed to overcome the voltage droop caused by the inductive effects of the PC board traces.

#### **ABSOLUTE MAXIMUM RATINGS\***

| Temperature under Bias                   |           |

|------------------------------------------|-----------|

| X2816C10°C                               | to +85°C  |

| X2816CI65°C to                           | o +135°C  |

| Storage Temperature65°C to               | o +150°C  |

| Voltage on any Pin with                  |           |

| Respect to V <sub>SS</sub> 1             | 1V to +7V |

| D.C. Output Current                      | 5mA       |

| Lead Temperature (Soldering, 10 seconds) | 300°C     |

#### \*COMMENT

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and the functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **RECOMMENDED OPERATING CONDITIONS**

| Temperature  | Min.  | Max.  |  |  |  |

|--------------|-------|-------|--|--|--|

| Commercial   | 0°C   | +70°C |  |  |  |

| Industrial   | −40°C | +85°C |  |  |  |

| 3852 PCM T02 |       |       |  |  |  |

| Supply Voltage | Limits  |

|----------------|---------|

| X2816C         | 5V ±10% |

|                |         |

3852 PGM T03.1

# D.C. OPERATING CHARACTERISTICS (Over recommended operating conditions unless otherwise specified.)

|                     |                                  | Limits |         |                    |       |                                                                                                   |

|---------------------|----------------------------------|--------|---------|--------------------|-------|---------------------------------------------------------------------------------------------------|

| Symbol              | Parameter                        | Min.   | Typ.(1) | Max.               | Units | Test Conditions                                                                                   |

| Icc                 | V <sub>CC</sub> Current (Active) |        | 70      | 110                | mA    | CE = OE = V <sub>IL</sub> All I/O's = Open Other Inputs = V <sub>CC</sub>                         |

| I <sub>SB1</sub>    | Vcc Current (Standby)            |        | 35      | 50                 | mA    | CE = V <sub>IH</sub> , OE = V <sub>IL</sub><br>All I/O's = Open<br>Other Inputs = V <sub>CC</sub> |

| ILI                 | Input Leakage Current            |        |         | 10                 | μΑ    | V <sub>IN</sub> = V <sub>SS</sub> to V <sub>CC</sub>                                              |

| ILO                 | Output Leakage Current           |        |         | 10                 | μΑ    | $V_{OUT} = V_{SS}$ to $V_{CC}$ , $\overline{CE} = V_{IH}$                                         |

| V <sub>IL</sub> (2) | Input LOW Voltage                | -1     |         | 0.8                | V     |                                                                                                   |

| V <sub>IH</sub> (2) | Input HIGH Voltage               | 2      |         | V <sub>CC</sub> +1 | V     |                                                                                                   |

| VoL                 | Output LOW Voltage               |        |         | 0.4                | V     | I <sub>OL</sub> = 2.1mA                                                                           |

| Voн                 | Output HIGH Voltage              | 2.4    |         |                    | V     | IOH = -400μA                                                                                      |

3852 PGM T02.2

**Notes:** (1) Typical values are for  $T_A = 25^{\circ}C$  and nominal supply voltage and are not tested.

(2) V<sub>IL</sub> min. and V<sub>IH</sub> max. are for reference only and are not tested.

## **ENDURANCE AND DATA RETENTION**

| Parameter         | Min.   | Max. | Unit        |

|-------------------|--------|------|-------------|

| Minimum Endurance | 10,000 |      | Cycles/Byte |

| Data Retention    | 100    |      | Years       |

3852 PGM T03

# **POWER-UP TIMING**

| Symbol               | Symbol Parameter            |   | Units |

|----------------------|-----------------------------|---|-------|

| t <sub>PUR</sub> (3) | Power-Up to Read Operation  | 1 | ms    |

| t <sub>PUW</sub> (3) | Power-Up to Write Operation | 5 | ms    |

3852 PGM T04

# **CAPACITANCE** $T_A = +25^{\circ}C$ , f = 1MHz, $V_{CC} = 5V$

| Symbol               | Symbol Test              |    | Units | Conditions           |

|----------------------|--------------------------|----|-------|----------------------|

| C <sub>I/O</sub> (3) | Input/Output Capacitance | 10 | pF    | $V_{I/O} = 0V$       |

| C <sub>IN</sub> (3)  | Input Capacitance        | 6  | pF    | V <sub>IN</sub> = 0V |

3852 PGM T05.1

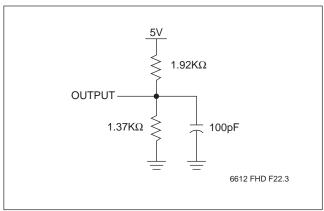

## A.C. CONDITIONS OF TEST

| Input Pulse Levels | 0V to 3V |

|--------------------|----------|

| Input Rise and     |          |

| Fall Times         | 5ns      |

| Input and Output   |          |

| Timing Levels      | 1.5V     |

3852 PGM T06.1

# MODE SELECTION

| CE | ŌĒ | WE | Mode                      | I/O    | Power   |

|----|----|----|---------------------------|--------|---------|

| L  | L  | Н  | Read                      | Dout   | Active  |

| L  | Н  | L  | Write                     | DIN    | Active  |

| Н  | X  | Х  | Standby and Write Inhibit | High Z | Standby |

| X  | L  | Х  | Write Inhibit             | _      |         |

| Х  | Х  | Н  | Write Inhibit             | _      | _       |

3852 PGM T07

$\textbf{Note:} \hspace{0.2in} \textbf{(3)} \hspace{0.2in} \textbf{This parameter is periodically sampled and not 100\% tested.}$

## **EQUIVALENT A.C. LOAD CIRCUITS**

# **A.C. CHARACTERISTICS** (Over recommended operating conditions unless otherwise specified.)

# **Read Cycle Limits**

|                      |                                    | X2816C-90 |      | X2816C-90 X28160 |      | 2 X2816C-15 |      | X2816C-20 |      |       |

|----------------------|------------------------------------|-----------|------|------------------|------|-------------|------|-----------|------|-------|

| Symbol               | Parameter                          | Min.      | Max. | Min.             | Max. | Min.        | Max. | Min.      | Max. | Units |

| t <sub>RC</sub>      | Read Cycle Time                    | 90        |      | 120              |      | 150         |      | 200       |      | ns    |

| t <sub>CE</sub>      | Chip Enable Access Time            |           | 90   |                  | 120  |             | 150  |           | 200  | ns    |

| tAA                  | Address Access Time                |           | 90   |                  | 120  |             | 150  |           | 200  | ns    |

| toE                  | Output Enable Access Time          |           | 60   |                  | 60   |             | 80   |           | 100  | ns    |

| t <sub>LZ</sub> (4)  | CE LOW to Active Output            | 0         |      | 0                |      | 0           |      | 0         |      | ns    |

| toLZ <sup>(4)</sup>  | OE LOW to Active Output            | 0         |      | 0                |      | 0           |      | 0         |      | ns    |

| t <sub>HZ</sub> (4)  | CE HIGH to High Z Output           |           | 50   |                  | 60   |             | 60   |           | 60   | ns    |

| t <sub>OHZ</sub> (4) | OE HIGH to High Z Output           |           | 50   |                  | 60   |             | 60   |           | 60   | ns    |

| tон                  | Output Hold from<br>Address Change | 0         |      | 0                |      | 0           |      | 0         |      | ns    |

3852 PGM T10.1

# **Read Cycle**

Notes: (4)  $t_{LZ}$  min.,  $t_{HZ}$ ,  $t_{OLZ}$ , and  $t_{OHZ}$  are periodically sampled and not 100% tested.  $t_{HZ}$  max. and  $t_{OHZ}$  max. are measured from the point when  $\overline{CE}$  or  $\overline{OE}$  return HIGH (whichever occurs first) to the time when the outputs are no longer driven.

# X2816C

# **Write Cycle Limits**

|                     |                     | X281 | X2816C-90 |      | X2816C-12,-15,-20 |       |

|---------------------|---------------------|------|-----------|------|-------------------|-------|

| Symbol              | Parameter           | Min. | Max.      | Min. | Max.              | Units |

| t <sub>WC</sub> (5) | Write Cycle Time    |      | 10        |      | 10                | ms    |

| tas                 | Address Setup Time  | 5    |           | 5    |                   | ns    |

| tah                 | Address Hold Time   | 80   |           | 100  |                   | ns    |

| tcs                 | Write Setup Time    | 0    |           | 0    |                   | ns    |

| tch                 | Write Hold Time     | 0    |           | 0    |                   | ns    |

| tcw                 | CE Pulse Width      | 80   |           | 100  |                   | ns    |

| toes                | OE HIGH Setup Time  | 10   |           | 10   |                   | ns    |

| toeh                | OE HIGH Hold Time   | 5    |           | 10   |                   | ns    |

| twp                 | WE Pulse Width      | 80   |           | 100  |                   | ns    |

| twpH                | WE HIGH Recovery    | 50   |           | 50   |                   | ns    |

| t <sub>DV</sub>     | Data Valid          |      | 100       |      | 100               | μs    |

| tos                 | Data Setup          | 35   |           | 50   |                   | ns    |

| t <sub>DH</sub>     | Data Hold           | 5    |           | 10   |                   | ns    |

| t <sub>DW</sub>     | Delay to Next Write | 10   |           | 10   |                   | μs    |

| tBLC                | Byte Load Cycle     | 1    | 100       | 1    | 100               | μs    |

3852 PGM T09.1

# $\overline{\text{WE}}$ Controlled Write Cycle

**Notes:** (5) t<sub>WC</sub> is the minimum cycle time to be allowed from the system perspective unless polling techniques are used. It is the maximum time the device requires to automatically complete the internal write operation.

# **CE** Controlled Write Cycle

## **Page Mode Write Cycle**

Notes: (6) Between successive byte writes within a page write operation,  $\overline{OE}$  can be strobed LOW: e.g. this can be done with  $\overline{CE}$  and  $\overline{WE}$  HIGH to fetch data from another memory device within the system for the next write; or with  $\overline{WE}$  HIGH and  $\overline{CE}$  LOW effectively performing a polling operation.

(7) The timings shown above are unique to page write operations. Individual byte load operations within the page write must conform to either the CE or WE controlled write cycle timing.

# DATA Polling Timing Diagram(10)

Note: (10) Polling operations are by definition read cycles and are therefore subject to read cycle timings.

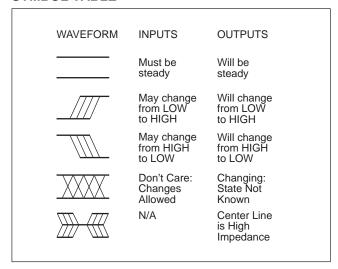

# **SYMBOL TABLE**

# X2816C

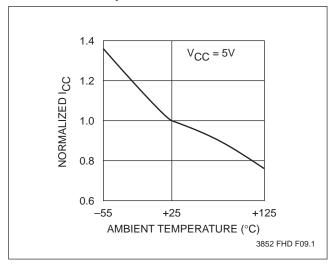

# Normalized Active Supply Current vs. Ambient Temperature

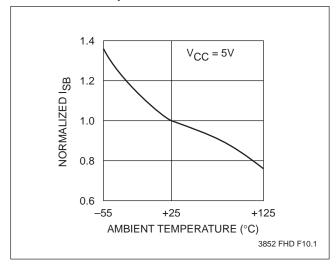

# Normalized Standby Supply Current vs. Ambient Temperature

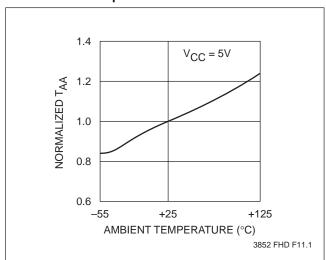

# Normalized Access Time vs. Ambient Temperature

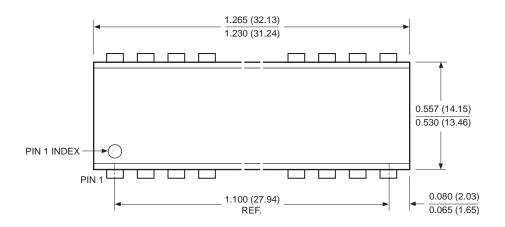

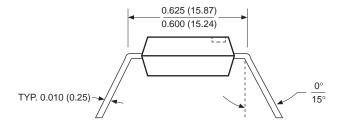

## 24-LEAD PLASTIC DUAL IN-LINE PACKAGE TYPE P

### NOTE:

- 1. ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)

2. PACKAGE DIMENSIONS EXCLUDE MOLDING FLASH

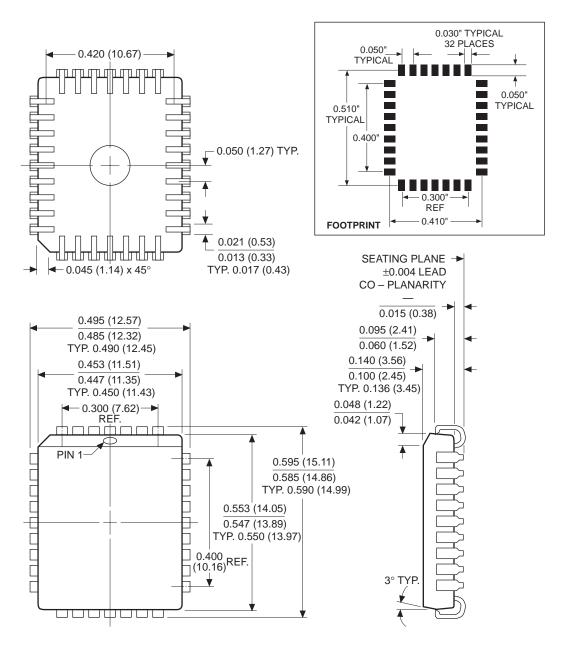

# 32-LEAD PLASTIC LEADED CHIP CARRIER PACKAGE TYPE J

#### NOTES:

- 1. ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)

- 2. DIMENSIONS WITH NO TOLERANCE FOR REFERENCE ONLY

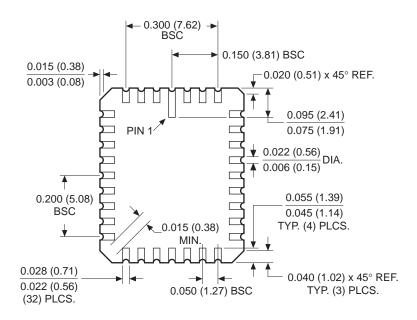

# 32-PAD CERAMIC LEADLESS CHIP CARRIER PACKAGE TYPE E

# NOTE:

- 1. ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)

- 2. TOLERANCE: ±1% NLT ±0.005 (0.127)

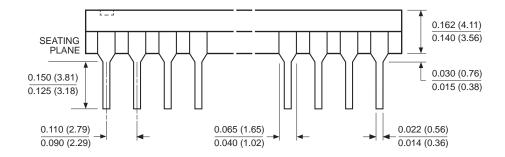

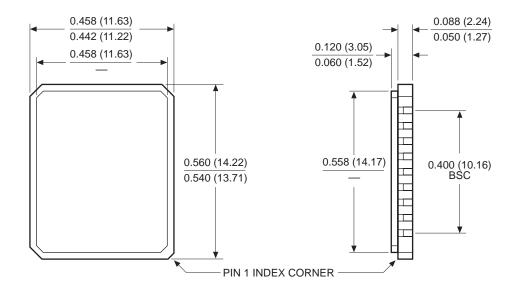

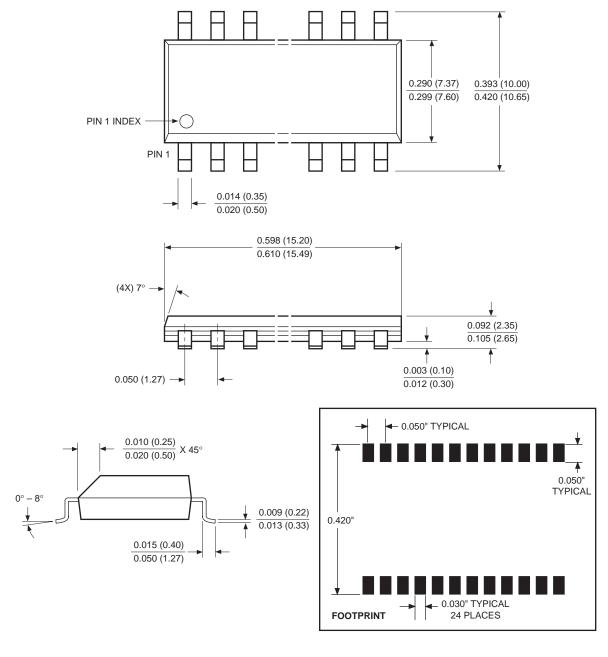

## 24-LEAD PLASTIC SMALL OUTLINE GULL WING PACKAGE TYPE S

NOTE: ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)

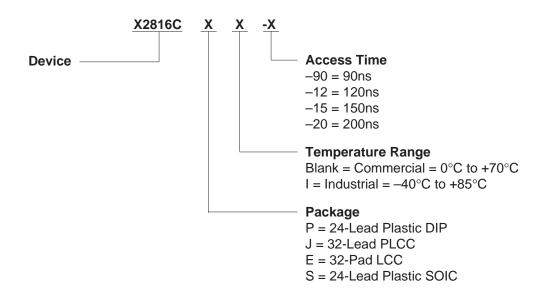

## **ORDERING INFORMATION**